- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC18F4539-I/ML (Microchip Technology)IC MCU FLASH 12KX16 EE A/D 44QFN

2002 Microchip Technology Inc.

Preliminary

DS30485A-page 103

PIC18FXX39

11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following

features:

16-bit timer/counter

(two 8-bit registers, TMR1H and TMR1L)

Readable and writable (both registers)

Internal or external clock select

Interrupt-on-overflow from FFFFh to 0000h

Figure 11-1 is a simplified block diagram of the Timer1

module.

Register 11-1 details the Timer1 control register, which

sets the Operating mode of the Timer1 module. Timer1

can be enabled or disabled by setting or clearing

control bit TMR1ON (T1CON<0>).

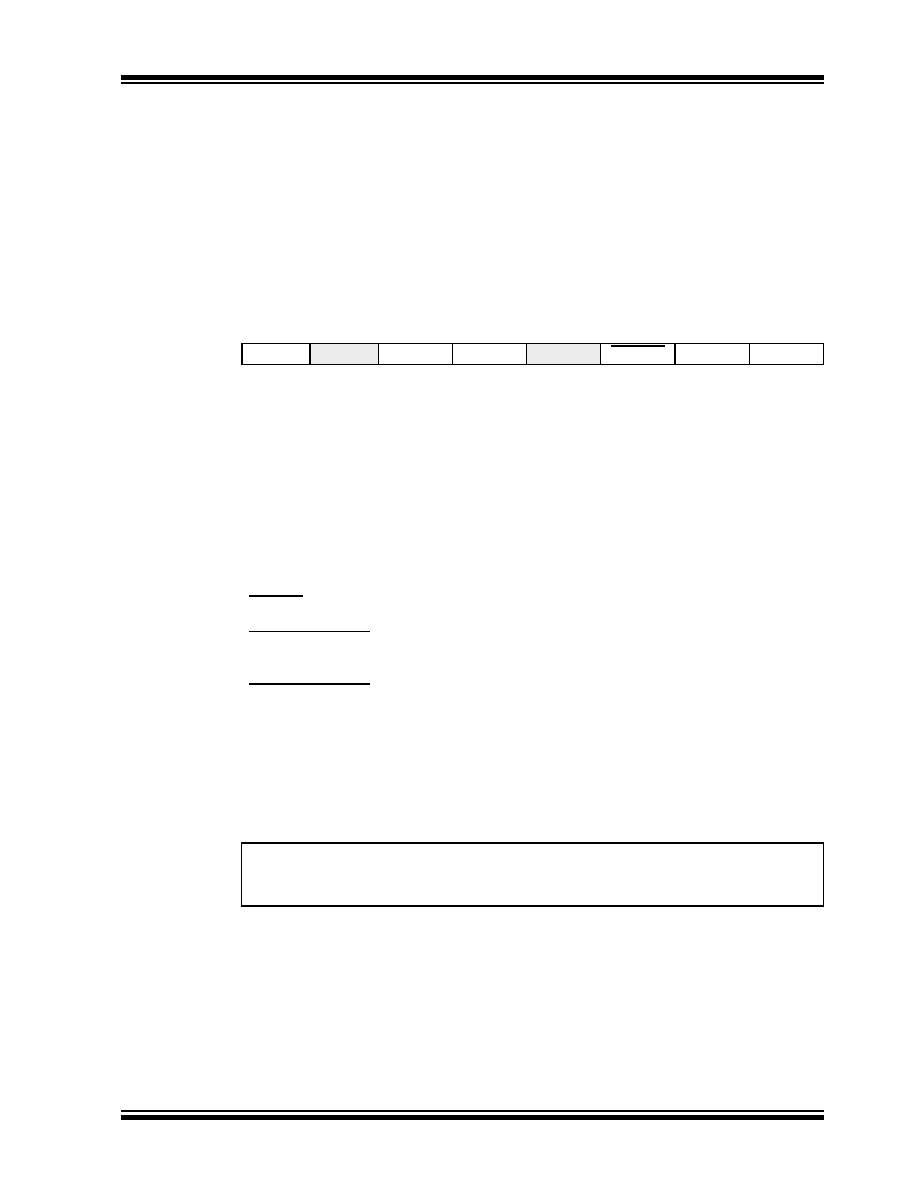

REGISTER 11-1:

T1CON: TIMER1 CONTROL REGISTER

R/W-0

U-0

R/W-0

U-0

R/W-0

RD16

—

T1CKPS1 T1CKPS0

—

T1SYNC

TMR1CS

TMR1ON

bit 7

bit 0

bit 7

RD16: 16-bit Read/Write Mode Enable bit

1

= Enables register read/write of Timer1 in one 16-bit operation

0

= Enables register read/write of Timer1 in two 8-bit operations

bit 6

Unimplemented: Read as '0'

bit 5-4

T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

11

= 1:8 Prescale value

10

= 1:4 Prescale value

01

= 1:2 Prescale value

00

= 1:1 Prescale value

bit 3

Unimplemented: Maintain as '0'

bit 2

T1SYNC: Timer1 External Clock Input Synchronization Select bit

When TMR1CS = 1:

1

= Do not synchronize external clock input

0

= Synchronize external clock input

When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1

TMR1CS: Timer1 Clock Source Select bit

1

= External clock from pin RC0/T13CKI (on the rising edge)

0

= Internal clock (FOSC/4)

bit 0

TMR1ON: Timer1 On bit

1

= Enables Timer1

0

= Stops Timer1

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

- n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4439-I/ML

IC MCU FLASH 6KX16 EE A/D 44QFN

PIC18F2439-I/SO

IC MCU FLASH 6KX16 EE A/D 28SOIC

PIC16F687-I/SO

IC PIC MCU FLASH 2KX14 20SOIC

PIC16F877AT-I/PTG

IC MCU FLASH 8KX14 W/AD 44 TQFP

PIC16F877A-I/LG

IC MCU FLASH 8KX14 W/AD 44PLCC

PIC12LC509AT-04I/MF

IC MCU OTP 1KX12 LV 8-DFN

PIC12C509AT-04I/MF

IC MCU OTP 1KX12 8-DFN

PIC24F08KL301-I/SS

IC MCU 16BIT 8KB FLASH 20-SSOP

相关代理商/技术参数

PIC18F4539-I/P

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4539 DIP40

PIC18F4539-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539IPT

制造商:MICRO CHIP 功能描述:NEW

PIC18F4539T-E/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-E/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT